Welcome to rd53a_emulator documentation!

For RD53A DEMO

- To get to YARR code base run cd Desktop/Yarr-develv2/Yarr/src

- Emulator bit files are saved in Desktop/Yarr-develv2/bits

- If the emulator stops working turn off the PC/ turn it back on and then reflash the emulator using vivado 2017.4

- To access 2017.4 run source ~/Xilinx/Vivado/2017.4/settings.sh

- To view data run an analogscan

- To adjust the amount of hit data produced change the value of HitOr0MaskDiff0

- To view the value of the registers on the emulator run rd53a_readreg

Build Info

- Targets Xilinx KC705 Kintex FPGA Board

- Vivado 2017.4

Description

Current Features/Non-features

- The main pieces of currently working functionality are listed below.

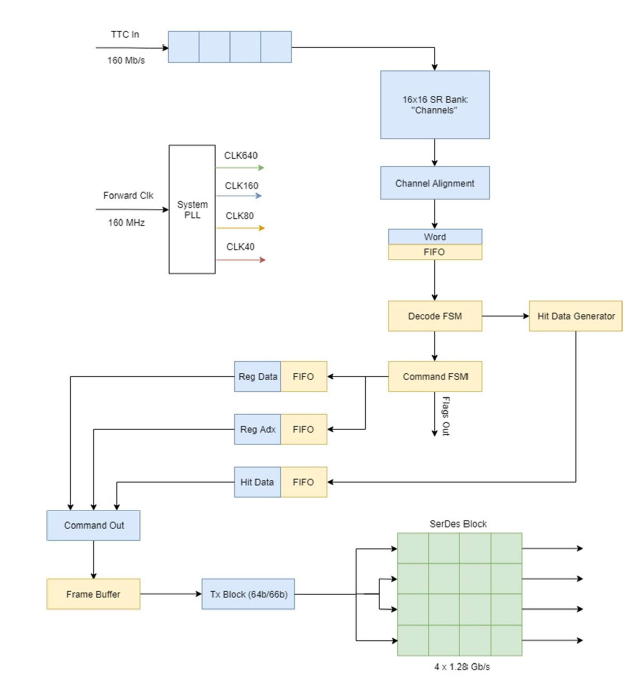

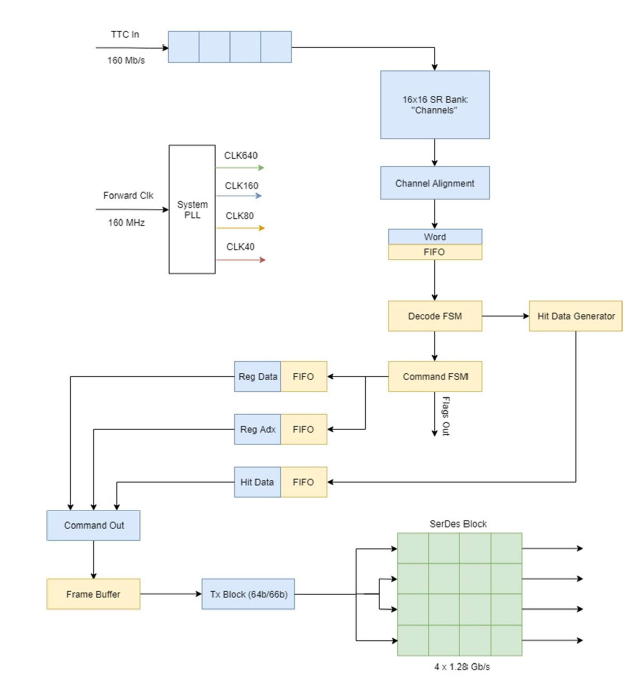

- Input data to the system is properly decoded using the custom rd53A protocol.

- Output data of the system is properly encoded using the aurora 64/66B protocal at 640 MHz.

- Reading and writing of global registers. The read out registers are sent through lane 0.

- Trigger commands output clumps of trigger data. The trigger data is based in real data collected at CERN. The shapes of the data consist mostly of small Tetris like pieces and lines. See usage examples for more information.

- ECR, BCR, and CAL commands are received by the system though currently have no external impact.

- The main non-features are listed below.

- Since this is a digital design project any RD53A features that involve analog circuitry such as the pixels have been greatly simplified or removed entirely.

- An example of a simplification is that the pixel data outputted by triggers is the result of random number generators and/or standarized data formats and is not produced by an emulation of individual pixels. Examples of analog features that have been removed include pixel calibration injection as well as the mechanics that allow the user to read/write to pixel registers and modify pixel configuration.

- As stated above ECR, BCR, and CAL commands are received by the system though currently have no external impact.

- The 160 MHz input clock is not derived from the input stream using clock data recovery and needs to be provided to the system as a seperate signal.

Planned Features/Updates

- The currently planned updates and upgrades to the system are listed below

- Developing compatiblity with the FELIX project.

- Bug fixes and adding user requested features to the RD53A

- Begin working on the RD53B version of the emulator